Contents lists available at ScienceDirect

## Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Self-aligned indium–gallium–zinc oxide thin-film transistors with SiN<sub>x</sub>/SiO<sub>2</sub>/SiN<sub>x</sub>/SiO<sub>2</sub> passivation layers

Rongsheng Chen \*, Wei Zhou, Meng Zhang, Hoi-Sing Kwok

Center for Display Research, Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong, Hong Kong

#### ARTICLE INFO

Article history: Received 19 December 2013 Received in revised form 3 March 2014 Accepted 29 May 2014 Available online 6 June 2014

Keywords: Thin-film transistors Amorphous indium-gallium-zinc oxide Self-aligned structure

#### ABSTRACT

Self-aligned top-gate amorphous indium–gallium–zinc oxide (a-IGZO) thin-film transistors (TFTs) with  $SiN_x/SiO_2/SiN_x/SiO_2$  passivation layers are developed in this paper. The resulting a-IGZO TFT exhibits high reliability against bias stress and good electrical performance including field-effect mobility of 5 cm²/Vs, threshold voltage of 2.5 V, subthreshold swing of 0.63 V/decade, and on/off current ratio of  $5 \times 10^6$ . With scaling down of the channel length, good characteristics are also obtained with a small shift of the threshold voltage and no degradation of subthreshold swing. The proposed a-IGZO TFTs in this paper can act as driving devices in the next generation flat panel displays.

© 2014 Elsevier B.V. All rights reserved.

### 1. Introduction

Recently, amorphous indium–gallium–zinc oxide (a-IGZO) thin-film transistors (TFTs) have become attractive for use as driving devices in large scale active matrix organic light emitting diode (AMOLED) applications, due to their higher mobility and larger area uniformity, as compared to amorphous silicon (a-Si) and polycrystalline silicon (p-Si) TFTs [1–4]. The conventional a-Si TFTs, which are used as switching devices in active-matrix liquid–crystal display, have the advantages of low manufacturing cost and large area uniformity. However, their low field-effect mobility (<1 cm²/Vs) may not be sufficient to drive AMOLED. Due to their high mobility (>50 cm²/Vs) and electrical stability, the conventional p-Si TFTs are currently used as driving devices in AMOLED displays. But the main issues are the non-uniformity of their field-effect mobility and threshold voltage, caused by the grain size and grain boundaries in p-Si thin films.

Conventional bottom-gate structure is widely studied for a-IGZO TFTs. But this structure is unsuitable for the integration of peripheral circuits for the system on glass and realization of high resolution high quality AMOLED displays, due to the high parasitic capacitance and poor scalability. Therefore, the development of self-aligned top-gate oxide TFT with good performance and high stability is necessary for AMOLED display applications. For example, several self-aligned structure oxide TFTs were reported, in which source and drain were doped by hydrogen diffusion from silicon nitride by plasma enhanced chemical vapor deposition (PECVD) [5,6] or by plasma treatment [7,8]. But it needs additional process step for the source and drain doping. Passivation layer has a major effect on the long-term stability for a-IGZO

TFTs. Single  $SiN_x$  layer deposited by PECVD has poor passivation ability for the oxygen or water penetration, which easily degrades the performance of a-IGZO TFTs [9].

In this paper, a self-aligned top-gate structure a-IGZO TFT with  $SiN_x/SiO_2/SiN_x/SiO_2$  passivation layers has been developed. The source and drain were doped n-type during over-etch of the gate dielectric with CHF<sub>3</sub>/O<sub>2</sub> plasma. The proposed a-IGZO TFTs show good electrical performance and high reliability against bias stress.

## 2. Experimental

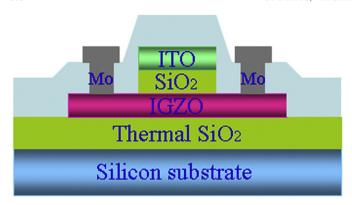

The cross-sectional schematic of the self-aligned top-gate type a-IGZO TFT studied in this paper is shown in Fig. 1.

A 100 nm thick a-IGZO active layer was first sputtered on thermally oxidized silicon wafer by DC magnetron sputtering using a target of  $In_2O_3$ : $Ga_2O_3$ :ZnO = 1:1:1 mol% in a mixed argon and oxygen ambient at room temperature. The deposition pressure and the power were 0.27 Pa and 120 W, respectively. After patterning this a-IGZO active layer by lift-off process, a 120 nm thick SiO2 layer as gate dielectric was deposited by PECVD from SiH<sub>4</sub> and N<sub>2</sub>O precursors on top of the a-IGZO layer at 300 °C. The gas flows of SiH<sub>4</sub> and N<sub>2</sub>O are 8 sccm and 1400 sccm, respectively. A 100 nm thick indium tin oxide (ITO), used as gate electrode, was sequentially sputtered at room temperature, and then defined by using photolithography and lift-off process. Then, the annealing process was executed at 200 °C for 30 min in a N<sub>2</sub> ambient. By reactive ion etching using CHF<sub>3</sub>/O<sub>2</sub> plasma, the SiO<sub>2</sub> gate dielectric was then self-aligned dry etched using ITO gate electrode pattern as a mask. After that, SiN<sub>x</sub>/SiO<sub>2</sub>/SiN<sub>x</sub>/SiO<sub>2</sub> multiple layers were deposited as passivation layers by PECVD at 150 °C. The deposition condition of SiO<sub>2</sub> is the same as that of the gate dielectric layer. The precursors for SiN<sub>x</sub> deposition are SiH<sub>4</sub> and NH<sub>3</sub>. The gas flows of SiH<sub>4</sub> and NH<sub>3</sub> are

<sup>\*</sup> Corresponding author. E-mail address: rschen@ust.hk (R. Chen).

Fig. 1. A cross-section schematic of the proposed a-IGZO TFT with self-aligned top-gate structure.

40 sccm and 30 sccm, respectively. After forming the contact holes, a 200 nm thick Mo layer was deposited by sputtering and patterned as gate/source/drain electrodes. The electrical properties of the a-IGZO TFTs were measured by using an HP4156A precision semiconductor parameter analyzer.

#### 3. Results and discussion

The field-effect mobility induced by the transconductance at a low drain voltage is given by

$$\mu_{\rm FE} = \frac{Lg_{\rm m}}{WC_{\rm OX}V_{\rm DS}} \tag{1}$$

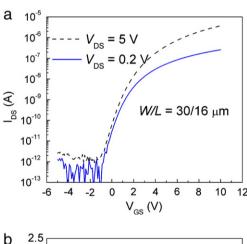

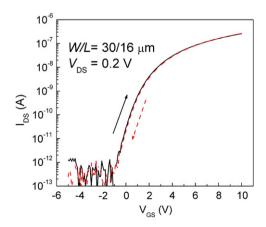

where  $g_{\rm m}$  and  $C_{\rm OX}$  are the transconductance and the gate insulator capacitance per unit area, respectively. Fig. 2 shows the typical transfer and output characteristics of the fabricated a-IGZO TFTs with a width

$\textbf{Fig. 2.} \ (a) \ Transfer \ characteristic \ and \ (b) \ output \ characteristic \ of \ the \ proposed \ self-aligned \ top-gate \ a-IGZO \ TFTs.$

to length ratio of 30/16  $\mu m$ . They exhibit good transfer TFT characteristics at a drain to source voltage ( $V_{\rm DS}$ ) of 0.2 V such as field-effect mobility of 5 cm<sup>2</sup>/Vs, threshold voltage of 2.5 V, subthreshold swing of 0.63 V/decade and on/off current ratio of 5  $\times$  10<sup>6</sup>. The output characteristic shows clear linear regions and does not show significant current crowding at low  $V_{\rm DS}$ , indicating that low series resistance in source/drain contacts was obtained.

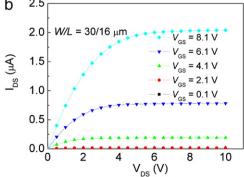

Fig. 3(a) shows the dependence of the channel length (L) on the field-effect mobility of the a-IGZO TFTs. As the channel length decreased from 16  $\mu$ m to 2  $\mu$ m, the maximum field-effect mobility of the a-IGZO TFTs decreased from 5 to 2.2 cm²/Vs. The decrease of the field-effect mobility for short channel devices is due to the existence of the source/drain series resistance  $R_{SD}$  on the potential distribution across the channel. Without considering this effect of  $R_{SD}$ , the field-effect mobility extracted using Eq. (1) underestimates the true field-effect mobility for the a-IGZO TFTs. In order to obtain the true field-effect mobility, the  $R_{SD}$  could be extracted by using the following relationship [10]:

$$\mu_{\rm FE} {\approx} \mu_0 \frac{L}{L + \mu_0 W C_{\rm OX} R_{\rm SD} (V_{\rm GS} - V_{\rm th})} \tag{2}$$

where  $\mu_{\rm FE}$  is the apparent field-effect mobility and  $\mu_0$  is the true field-effect mobility of the a-IGZO material. The  $R_{\rm SD}$  for the a-IGZO TFTs was extracted to be 115 k $\Omega$  from the fitting of the apparent field-effect mobility in Fig. 3(b) using Eq. (2). The width-normalized  $R_{\rm SD}W$  was 345  $\Omega$ cm. As a result, the true channel mobility was extracted to be 6.1 cm<sup>2</sup>/Vs for the a-IGZO TFTs.

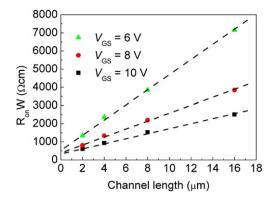

The  $R_{\rm SD}$  was also extracted by determining the device on-resistance  $R_{\rm on}$  from the linear region of the transfer characteristics and plotting the width normalized  $R_{\rm on}W$  as a function of the L for different gate voltages [11]. Fig. 4 shows the width normalized  $R_{\rm on}W$  as a function of L at different gate voltage at  $V_{\rm DS}=0.2$  V for the a-IGZO TFTs. The  $R_{\rm SD}W$  for the a-IGZO TFTs, which is extracted at the y-axis intercept of the extrapolated linear fit of  $R_{\rm on}W$  versus L, is approximately 300  $\Omega$ cm for  $V_{\rm GS}=10$  V,

**Fig. 3.** (a) Dependence of channel length L on the field-effect mobility  $\mu_{\rm FE}$  for the a-IGZO TFTs. (b) The field-effect mobility  $\mu_{\rm FE}$  at various channel length L and the fitting result considering  $R_{\rm SD}$  (red dash curve).

Channel length (µm)

**Fig. 4.** Width normalized device on-resistance  $R_{on}W$  as a function of L.

which is similar to that of bottom-gate a-IGZO TFTs [3]. The  $R_{\rm SD}W$  value extracted by this method is similar to that extracted from the fitting result in Fig. 3(b) using Eq. (2). This low source/drain series resistance is caused by the surface modification and hydrogen diffusion into source/drain area during over-etch of the gate oxide  ${\rm SiO_2}$  dry-etching process with  ${\rm CHF_3/O_2}$  plasma and silicon nitride deposition process with  ${\rm SiH_4}$  and  ${\rm NH_3}$  plasma. Hydrogen diffusion into the a-IGZO thin film can cause low resistivity of the a-IGZO. Hydrogen is an n-type dopant for a-IGZO thin film. The sheet resistance of a-IGZO thin film after dry-etching process of the gate oxide and deposition process of silicon nitride was found to be as low as 3 k $\Omega$ /sq. Different from earlier reports [7,8], no further plasma treatment process is needed for the source/drain area

To study the short channel effects, the transfer characteristic (at  $V_{DS}$  = 5 V) of the a-IGZO TFTs with different channel lengths ( $L=16,\,8,\,4,\,2\,\mu m$ ) is compared in Fig. 5. From Fig. 5, a small change of the threshold voltages and no degradation of subthreshold swing with different

**Fig. 5.** (a) Transfer characteristics of the a-IGZO TFTs with the same channel width but different channel lengths. (b) Threshold voltage and subthreshold swing at various channel lengths for the a-IGZO TFTs.

channel lengths were obtained, which indicates good stability against short channel effects. This good scaling down behavior implicates small lateral diffusion of the hydrogen from the source/drain area to the channel region. This characteristic is much better than that reported earlier [6,12].

To investigate the effect of  $SiO_2$  gate dielectric and its interface with active layer, the hysteresis of a-IGZO TFT was examined, as shown in Fig. 6. A very small shift of threshold voltage for the hysteresis loop indicated that little electrons were trapped at or near the  $SiO_2/IGZO$  interface or within the a-IGZO channel layer.

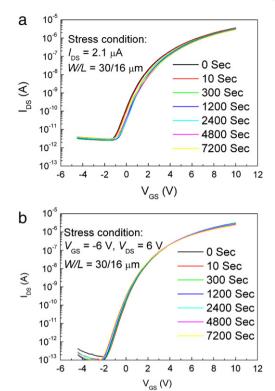

Channel protection with passivation layer is crucial for improving the long-term stability of a-IGZO TFTs. Conventional single silicon nitride passivation layer deposited by PECVD easily degrades the a-IGZO TFTs performance due to its poor passivation ability for the oxygen or water penetration [9]. SiO<sub>2</sub> film deposited by PECVD has high barrier property and very low hydrogen content. Dielectric SiN<sub>x</sub> or SiO<sub>2</sub> thin film deposited by PECVD at low temperature usually has pinhole defects inside the film, which will degrade the passivation quality of the film. The pinholes in one layer could be covered by another layer. The stack of four layers of SiN<sub>x</sub>/SiO<sub>2</sub>/SiN<sub>x</sub>/SiO<sub>2</sub> has better passivation quality than one or two layers. Therefore, SiN<sub>x</sub>/SiO<sub>2</sub>/SiN<sub>x</sub>/SiO<sub>2</sub> multiple layers were used as passivation layers in this work. Fig. 7 shows the shift of transfer characteristic of a-IGZO TFT after bias stress. The bias stress condition was set to two types of the constant current bias ( $I_{DS} = 2.1 \,\mu\text{A}$ ), as shown in Fig. 7(a) and the negative gate bias ( $V_{CS} = -6 \text{ V}$ ,  $V_{DS} = 6 \text{ V}$ ), as shown in Fig. 7(b). From these two experiments, the shift of threshold voltage after 7200 s of both bias stress were below 0.4 V.

### 4. Conclusion

Self-aligned top-gate a-IGZO TFTs are developed in this paper. The resulting transistor exhibits field-effect mobility of 5 cm²/Vs, threshold voltage of 2.5 V, subthreshold swing of 0.63 V/decade and on/off current ratio of  $5\times 10^6$ . With scaling down the channel length, good characteristics are also obtained with small change of the threshold voltages and no degradation of subthreshold swing. Under constant current bias and negative gate bias stress, the shift of threshold voltage after 7200 s was below 0.4 V, due to good  $SiN_{\rm x}/SiO_2/SiN_{\rm x}/SiO_2$  multiple passivation layers. The proposed top-gate a-IGZO TFTs in this paper can act as driving devices in the next generation flat panel displays.

## Acknowledgment

This research is supported by Hong Kong Government Research Grants Council under Theme-Based Research Scheme T23-713/11-1.

Fig. 6. Hysteresis characteristic of the a-IGZO TFTs.

**Fig. 7.** Evolution of the transfer characteristics as a function of (a) constant current stress time and (b) negative gate bias stress time.

### References

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432 (7016) (2004) 488.

- [2] E.M.C. Fortunato, P.M.C. Barquinha, A.C.M.B.G. Pimentel, A.M.F. Goncalves, A.J.S. Marques, R.F.P. Martins, L.M.N. Pereira, Wide-bandgap high-mobility ZnO thin-film transistors produced at room temperature, Appl. Phys. Lett. 85 (2004) 2541.

- [3] M. Kim, J. Jeong, H. Lee, T. Ahn, H. Shin, J. Park, J. Jeong, Y. Mo, H. Kim, High mobility bottom gate InGaZnO thin film transistors with SiOx etch stopper, Appl. Phys. Lett. 90 (2007) 212114.

- [4] L.F. Lan, J.B. Peng, High-performance indium-gallium-zinc oxide thin-film transistors based on anodic aluminum oxide, IEEE Trans. Electron Devices 58 (2011) 1452.

- [5] C.H. Wu, H.H. Hsieh, C.W. Chien, C.C. Wu, Self-aligned top-gate coplanar In–Ga–Zn-O thin-film transistors, J. Disp. Technol. 5 (2009) 515.

- [6] D.H. Kang, I. Kang, S.H. Ryu, J. Jang, Self-aligned coplanar a-IGZO TFTs and application to high-speed circuits, IEEE Electron Device Lett. 32 (2011) 1385.

- [7] J. Park, I. Song, S. Kim, S. Kim, C. Kim, J. Lee, H. Lee, E. Lee, H. Yin, K. Kim, K. Kwon, Y. Park, Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors, Appl Phys. Lett. 93 (2008) 053501.

[8] S. Kim, J. Park, C. Kim, I. Song, S. Kim, S. Park, H. Yin, H. Lee, E. Lee, Y. Park, Source/

- [8] S. Kim, J. Park, C. Kim, I. Song, S. Kim, S. Park, H. Yin, H. Lee, E. Lee, Y. Park, Source/drain formation of self-aligned top-gate amorphous GalnZnO thin-film transistors by NH<sub>3</sub> plasma treatment, IEEE Electron Device Lett. 30 (2009) 374.

- [9] T. Arai, T. Sasaoka, Emergent oxide TFT technologies for next-generation AMOLED displays, Proc. SID Digest, 2011, p. 710.

- [10] K.Y. Chan, E. Bunte, H. Stiebig, D. Knipp, Influence of contact effect on the performance of microcrystalline silicon thin-film transistors, Appl. Phys. Lett. 89 (2006) 203509.

- [11] J. Zaumseil, K.W. Baldwin, J.A. Rogers, Contact resistance in organic transistors that use source and drain electrodes formed by soft contact lamination, J. Appl. Phys. 93 (2003) 6117.

- [12] E.N. Cho, J.H. Kang, I. Yun, Contact resistance dependent scaling-down behavior of amorphous InGaZnO thin-film transistors, Curr. Appl. Phys. 11 (2011) 1015.