Home Search Collections Journals About Contact us My IOPscience

High-performance polycrystalline silicon thin-film transistors integrating sputtered aluminumoxide gate dielectric with bridged-grain active channel

This article has been downloaded from IOPscience. Please scroll down to see the full text article.

2013 Semicond. Sci. Technol. 28 115003

(http://iopscience.iop.org/0268-1242/28/11/115003)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 202.40.139.167

The article was downloaded on 19/09/2013 at 02:05

Please note that terms and conditions apply.

Semicond. Sci. Technol. 28 (2013) 115003 (5pp)

# High-performance polycrystalline silicon thin-film transistors integrating sputtered aluminum-oxide gate dielectric with bridged-grain active channel

Meng Zhang<sup>1</sup>, Wei Zhou, Rongsheng Chen, Man Wong and Hoi-Sing Kwok

Center for Display Research and Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong

E-mail: zhangmeng@ust.hk

Received 30 May 2013, in final form 31 July 2013 Published 18 September 2013 Online at stacks.iop.org/SST/28/115003

#### **Abstract**

Polycrystalline silicon thin-film transistors (TFTs) integrating sputtered  $Al_2O_3$  gate dielectric with bridged-grain active channel are demonstrated. The proposed TFTs exhibit excellent device performance in terms of smaller threshold voltage, steeper subthreshold swing and higher on-current/off-current ratio. More importantly, the mobility of the proposed TFT is 5.5 times that of conventional TFTs with  $SiO_2$  gate dielectric. All of these results suggest that the proposed TFT is a good choice for low-power and high-speed driving circuits in display application.

(Some figures may appear in colour only in the online journal)

#### 1. Introduction

Polycrystalline silicon (poly-Si) thin-film transistors (TFTs) have received considerable research interest due to their high carrier mobility, which could provide possible solutions for the integration of peripheral circuit and active matrix in display applications [1]. High-performance poly-Si TFTs with low operating voltage, steep subthreshold swing (SS) and large on-current/off-current  $(I_{on}/I_{off})$  ratio are thus desired to accomplish the low-power and high-speed display driving circuits. However, poly-Si thin films, especially for solid-phase-crystallized (SPC) film, have numerous grain boundaries (GBs) inside [2, 3], resulting in large threshold voltage ( $V_{\text{th}}$ ), poor SS and small  $I_{\text{on}}/I_{\text{off}}$  ratio in poly-Si TFTs. Scaling down the conventional gate dielectrics (i.e., SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>) can increase gate capacitance and satisfy some demands listed above but would cause a higher gate-leakage current and bring more serious reliability issues due to the thinner oxide [4]. To maintain the physical gate dielectric thickness while increasing gate capacitance, several high-k gate dielectric materials [4–7], such as Al<sub>2</sub>O<sub>3</sub> [4], HfO<sub>2</sub> [5], Pr<sub>2</sub>O<sub>3</sub> [6] and Y<sub>2</sub>O<sub>3</sub> [7], are applied into the poly-Si TFTs to improve device electrical characteristics. Nevertheless, poly-Si TFTs with high-k gate dielectrics suffer from a more undesirable gate-induced drain leakage (*GIDL*) current due to the larger permittivity of high-k gate dielectrics [4–12].

In this work, poly-Si TFTs integrating a high-k Al<sub>2</sub>O<sub>3</sub> gate dielectric with bridged-grain (BG) [2] SPC active channel is first demonstrated. By employing Al<sub>2</sub>O<sub>3</sub> gate dielectric and BG active channel, the SPC poly-Si TFTs exhibit outstanding electrical characteristics in terms of smaller  $V_{\rm th}$ , steeper SS, larger  $I_{\rm on}/I_{\rm off}$  ratio and especially much lower GIDL current, compared to the control SPC TFTs. It is also worth mentioning that the maximum field-effect mobility ( $\mu_{\rm FE}$ ) of proposed TFTs is up to 47.92 cm<sup>2</sup> Vs<sup>-1</sup>, which is 4.5 times larger than that of SPC poly-Si TFTs with low-pressure chemical vapor deposition (LPCVD) SiO<sub>2</sub> gate dielectric and 1.9 times larger than that of SPC poly-Si TFT with sputtered Al<sub>2</sub>O<sub>3</sub> gate dielectric.

<sup>&</sup>lt;sup>1</sup> Author to whom any correspondence should be addressed.

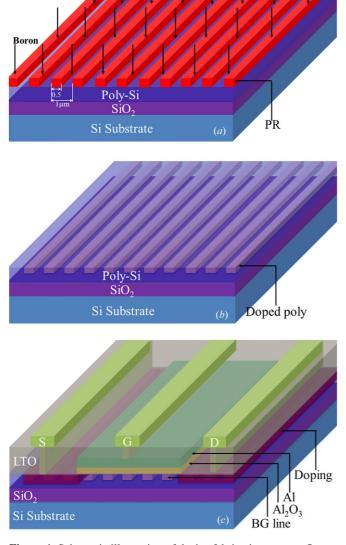

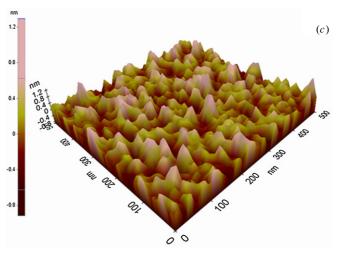

**Figure 1.** Schematic illustration of device fabrication process flow of BG SPC TFT with  $Al_2O_3$ . (a) Pattern formation of BG lines. The red cuboids stand for photoresist. (b) The schematic of active channel with selective boron doped BG lines. (c) Schematic of the proposed BG SPC TFTs with  $Al_2O_3$  gate dielectric.

### 2. Experimental

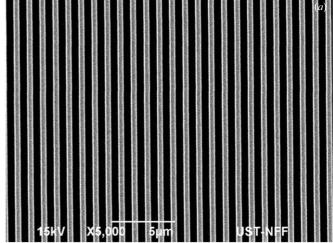

TFTs used in this study were in conventional self-aligned top-gate structure. A schematic illustration of device fabrication process flow is shown in figure 1. First, a layer of 100-nm-thick amorphous-Si (a-Si) was deposited on an oxidized silicon wafer by LPCVD. Then the a-Si layer is crystallized by SPC method at 600 °C for 24 h in  $N_2$  ambient. After crystallization, a layer of photoresist (PR) was coated on the wafer and then patterned into a series of lines as shown in figure 1(a). The red cuboids stand for remaining PR after photolithography. The scanning electron microscope (SEM) image and atomic force microscope (AFM) image of BG line pattern after lithography are shown in figures 2(a) and (b), respectively. It can be observed that the period of BG lines is about  $1~\mu$ m and the PR-covered line ratio in one period is about 50%, as also shown in

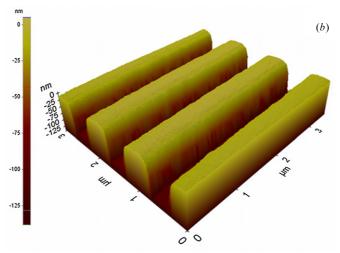

**Figure 2.** (a) SEM image and (b) AFM image of BG line pattern after lithography. (c) AFM image of the 70-nm-thick Al<sub>2</sub>O<sub>3</sub> film sputtered on the bare Si wafer.

figure 1(a). Boron implantation with a dose of  $10^{15}$  cm<sup>-2</sup> was then performed. After the implantation, the PR is removed. Subsequently, the doped BG poly-Si lines inside the poly-Si thin film were formed as shown in figure 1(b). Then the active layer was defined and patterned by photolithography

and wet etching. Next, 70-nm-thick Al<sub>2</sub>O<sub>3</sub> was deposited using reactive dc magnetron sputtering method in a mixed Ar and O<sub>2</sub> ambient at room temperature. The deposition pressure and the power were 3 mTorr and 120 W, respectively. The AFM image of the 70-nm-thick Al<sub>2</sub>O<sub>3</sub> film sputtered on bare Si wafer is shown in figure 2(c). The root mean square surface roughness is 0.489 nm. The measured capacitance density of Si/53-nm-thick-Al<sub>2</sub>O<sub>3</sub>/Al capacitor with area of  $50 \ \mu \text{m} \times 50 \ \mu \text{m}$  is about 130 nF cm<sup>-2</sup>. The permittivity of sputtered Al<sub>2</sub>O<sub>3</sub> thin film is estimated to be 8.14, which is about two times higher than that of SiO<sub>2</sub> deposited by LPCVD. After the gate dielectric deposition, sputtering of 300-nm-thick pure Al as gate electrode was performed, followed by gate patterning. Then a self-aligned boron implantation with a dose of  $4 \times 10^{15}$  cm<sup>-2</sup> was done to form the source and drain. Then 500-nm-thick low-temperature oxide was deposited by LPCVD. Contact holes were opened and then sputtering of 700-nm-thick Al doped with 1% Si was performed, followed by electrode patterning. Finally, wafers were sintered in forming gas at 420 °C. The fabricated TFTs are named BG SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric. For comparison, another two kinds of TFTs were fabricated at the same time. One is conventional SPC poly-Si TFTs with 70-nm-thick-sputtered-Al<sub>2</sub>O<sub>3</sub> gate dielectric, named SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric and the other is conventional SPC poly-Si TFT with 70-nm-thick-LPCVD-SiO<sub>2</sub> gate dielectric, named SPC TFT with SiO<sub>2</sub> gate dielectric. For all TFTs, after the fabrication, no further additional treatments are performed.

For characterization, the Agilent 4156A semiconductor parameter is used to test the device electrical performance. All TFTs used in this work have 24  $\mu$ m in width (W) and 10  $\mu$ m in length (L). The  $\mu$ FE is extracted from the following expressions [2],

$$\mu_{\rm FE} = \frac{LdG_m}{W\varepsilon_{\rm ox}V_{\rm ds}}$$

$$G_m = \operatorname{Max}\left(\frac{\mathrm{d}I_{\mathrm{ds}}}{\mathrm{d}V_{\mathrm{gs}}}\right)$$

where d,  $\varepsilon_{\rm ox}$ ,  $I_{\rm ds}$  and  $G_m$  are physical gate dielectric thickness, gate dielectric permittivity, drain current and maximum of transconductance at  $V_{\rm ds}=-0.1$  V. The  $V_{\rm th}$  is determined by the interception of linear extrapolation of a transfer curve at  $V_{\rm ds}=-0.1$  V. The SS is also extracted at  $V_{\rm ds}=-0.1$  V from the slope of log  $|I_{\rm on}|$  in the subthreshold region. The  $I_{\rm on}/I_{\rm off}$  ratio equals to maximum current over minimum current within the measured range. The GIDL current is defined at  $V_{\rm ds}=-5$  V and  $V_{\rm gs}=5$  V.

#### 3. Results and discussion

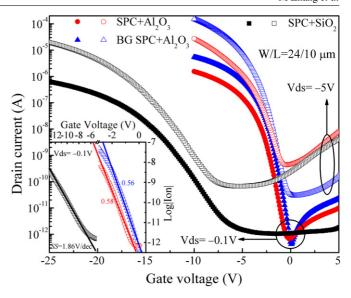

The transfer characteristic of SPC TFT with  $SiO_2$  gate dielectric, SPC TFT with  $Al_2O_3$  gate dielectric and BG SPC TFT with  $Al_2O_3$  gate dielectric measured at  $V_{\rm ds}=-0.1$  and -5 V are shown in figure 3. The inset is  $log I_{\rm onl}$  curves dependent on gate voltage plotted in subthreshold region for different devices. Compared to SPC TFT with  $SiO_2$  gate dielectric (dark lines), all electrical parameters of SPC TFT with  $Al_2O_3$  gate dielectric (red lines) are

**Figure 3.** Transfer characteristics of SPC TFT with SiO<sub>2</sub> gate dielectric, SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric and BG SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric measured at  $V_{\rm ds} = -1$  and -5 V. The inset is  $\log |I_{\rm on}|$  curves of subthreshold region for different devices.

improved, except GIDL current. By replacing  $SiO_2$  dielectric with  $Al_2O_3$  dielectric, the  $\mu_{FE}$  increases from 8.74 to  $16.67~\rm cm^2~\rm V s^{-1}$ , the  $V_{\rm th}$  reduces from  $-19.12~\rm to~-4.37~\rm V$  and the SS decreases from 1.86 to 0.58 V dec<sup>-1</sup>. However, the GIDL current increases from 4.20 to 8.09 nA. The related parameters are summarized in table 1. The thinner equivalent oxide thickness with the same physical thickness of high-k  $Al_2O_3$  gate dielectric increases gate capacitance and improves the mobile carrier density, resulting in smaller  $V_{\rm th}$  and SS [4–7]. Regarding the leakage mechanism of poly-Si TFTs [8–12], the  $I_{\rm off}$  at high  $|V_{\rm ds}|$  is strongly dependent on the peak electric field  $E_p$  at the drain junction, which can be expressed by the following formulas,

$$I_{\rm off} \propto \exp(\sqrt{E_p})$$

$$E_p = \frac{(V_{\rm gs} - V_{\rm ds} - V_{\rm fb})\varepsilon_{\rm ox}}{{\rm d}\varepsilon_{\rm Si}}$$

where  $\varepsilon_{Si}$  and  $V_{fb}$  are Si permittivity and flat-band voltage. Poly-Si TFT with high-k dielectric will bring larger  $E_p$ , giving rise to a rapid increase in off-state current.

To suppress this high off leakage current, BG active channel as described above is employed. As shown in figure 3, compared to SPC TFT with  $Al_2O_3$  gate dielectric (red lines), the *GIDL* current of BG SPC TFT (blue lines) is greatly reduced by more than 43.9 times. For the BG SPC TFTs, a number of submicron-scale reverse-biased junctions are formed when the channel is in off-state region. The  $E_p$  near the drain junction can be partially distributed to the edge of BG lines [2], leading to reduced  $E_p$  and decreased *GIDL* current. Besides *GIDL* suppression, the  $\mu_{FE}$ ,  $V_{th}$ , SS and  $I_{on}/I_{off}$  ratio of BG SPC TFT with  $Al_2O_3$  gate dielectric are also improved. The  $\mu_{FE}$  is enhanced to 47.92 cm<sup>2</sup> Vs<sup>-1</sup>, which is 1.8 times larger than that of SPC TFT with  $SIO_2$  gate dielectric. The  $V_{th}$  keeps decreasing to -3.85 V while the SS reduces a little, from

**Table 1.** Comparison of device parameters for different kinds of SPC TFTs at  $|V_{ds}| = 0.1 \text{ V}$ .

| Parameters                                                                                                         | SPC TFT $+$ 50 nm SiO <sub>2</sub> [7]     | $SPC TFT + SiO_2$                               | SPC TFT $+ Al_2O_3$                             | $BG SPC TFT + Al_2O_3$                          |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| $\mu_{\rm FE}  ({\rm cm^2  Vs^{-1}})$ $ V_{\rm th}   ({\rm V})$ $SS  ({\rm V  dec^{-1}})$ $I_{\rm on}/I_{\rm off}$ | 11<br>12<br>2.06<br>4.65 × 10 <sup>6</sup> | 8.74<br>19.12<br>1.86<br>6.13 × 10 <sup>5</sup> | 16.67<br>4.37<br>0.58<br>2.31 × 10 <sup>6</sup> | 47.92<br>3.85<br>0.56<br>1.30 × 10 <sup>7</sup> |

| $I_{\text{on}}/I_{\text{off}} (@V_{\text{ds}} = -5 \text{ V})$<br>GIDL (nA)                                        |                                            | $2.93 \times 10^5$ $4.20$                       | $6.23 \times 10^4$ $8.09$                       | $5.24 \times 10^6$ $0.18$                       |

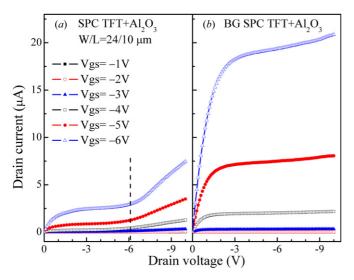

**Figure 4.** Output characteristics of (a) SPC TFT and (b) BG SPC TFT, measured at different  $V_{\rm gs}$ .

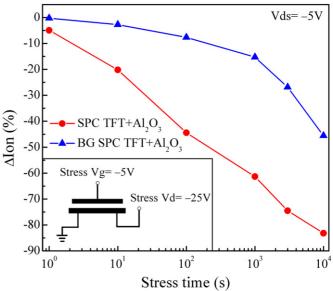

0.58 to 0.56 V dec<sup>-1</sup>. The  $I_{\rm on}/I_{\rm off}$  ratio of BG SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric at  $V_{\rm ds} = -0.1 \text{ V}$  is 1.3  $\times$  10<sup>7</sup>, which is 4.6 times larger than that of SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric and 20.2 times larger than that of SPC TFT with SiO<sub>2</sub> gate dielectric. The detailed parameter data are summarized in table 1. Compared to the SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric, the improved on-state characteristics of BG SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric is due to the BG lines, which links the grains, provides shortcuts for carriers and helps the carriers to find the more conductive path [2]. The output characteristics of SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric and BG SPC TFT with  $Al_2O_3$  gate dielectric measured at different  $V_{gs}$  are shown in figures 4(a) and (b), respectively. The saturation current is greatly enhanced by more than four times, consistent to the transfer curve. It is also noted that for SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric the kink current can be clearly observed at  $V_{\rm ds} \approx -6$  V and  $V_{\rm gs} = -6$  V, while for BG SPC TFT with Al<sub>2</sub>O<sub>3</sub> gate dielectric no kink current is observed at the same measurement range, implying the better hot carrier (HC) reliability of BG SPC TFT [13, 14]. To verify the better HC reliability of BG SPC TFT, HC stress test is performed on BG SPC TFT with Al<sub>2</sub>O<sub>3</sub> and SPC TFT with Al<sub>2</sub>O<sub>3</sub> as shown in figure 5. The stress condition is shown in the inset. It can be clearly observed that BG SPC TFT degenerates more slowly compared to normal SPC TFT at the same HC stress, consistent to kink effect suppression by BG structure in output curve.

**Figure 5.**  $I_{on}$  degradation of BG SPC TFT with  $Al_2O_3$  and SPC TFT with  $Al_2O_3$  under HC stress. The inset is the stress condition.

#### 4. Summary

High-performance SPC poly-Si TFTs with a high-k Al<sub>2</sub>O<sub>3</sub> gate dielectric and BG active channel is demonstrated. The TFTs show outstanding electrical performance in terms of larger  $\mu_{\rm FE}$ , smaller  $V_{\rm th}$ , steeper SS and larger  $I_{\rm on}/I_{\rm off}$  ratio compared to the control TFTs, which can satisfy the needs of peripheral driving circuit applications with low power and high speed.

## Acknowledgment

This project was supported by Hong Kong Research Grants Council Theme Based Research Scheme Project No. T23-713/11-1.

## References

- [1] Ohshima H and Morozumi S 1989 IEDM p 157

- [2] Zhou W, Meng Z, Zhao S, Zhang M, Chen R, Wong M and Kwok H S 2012 IEEE Electron Device Lett. 33 1414

- [3] Meng Z, Wang M and Wong M 2000 IEEE Trans. Electron Devices 47 404

- [4] Wilka G D, Wallace R M and Anthony J M 2001 J. Appl. Phys. 89 5243

- [5] Lin C P, Tsui B Y, Yang M J, Huang R H and Chien C H 2006 IEEE Electron Device Lett. 27 360

- [6] Chang C W, Deng C K, Huang J J, Chang H R and Lei T F 2008 IEEE Electron Device Lett. 29 96

- [7] Pan T M and Chang C J 2011 Semicond. Sci. Technol. 26 075004

- [8] Zhang M, Wang M, Lu X, Wong M and Kwok H S 2012 IEEE Trans. Electron Devices 59 1730

- [9] Yang M J, Chien C H, Lu Y H, Luo G L, Chiu S C, Lou C C and Huang T Y 2007 IEEE Electron Device Lett. 28 902

- [10] Yeh C F, Lin S S, Yang T Z, Chen C L and Yang Y C 1994 IEEE Trans. Electron Devices 41 173

- [11] Yazaki M, Takenaka S and Ohshima H 1992 Japan. J. Appl. Phys. 31 206

- [12] Hack M, Wu I W, King T J and Lewis A G 1993 IEDM p 385

- [13] Koyanagi M, Kurino H, Hashimoto T, Mori H, Hata K, Hirumat Y, Fujimon T, Wu I W and Lewis A G 1991 IEDM p 571

- [14] Zhang M, Wang M, Wang H and Zhou J 2009 *IEEE Trans.* Electron Devices **56** 2726